Модель: VariableRateLimiter

Библиотека: Signals

Имя на уровне решателя: TSIG10

Аннотация: Модель переменного ограничения скорости сигнала

Обозначение:

Описание модели

№ |

Обозначение порта |

Тип |

Наименование порта |

|---|---|---|---|

1 |

Port1 |

base.DOF1 |

Сигнальный входной порт |

2 |

Port2 |

base.DOF1 |

Сигнальный входной порт |

3 |

Port3 |

base.DOF1 |

Сигнальный входной порт |

4 |

Port4 |

base.DOF1 |

Сигнальный выходной порт |

№ |

Параметр |

Тип |

Описание |

Значение по умолч. |

|---|---|---|---|---|

1 |

K |

base.real |

Коэффициент усиления сигнала |

1 |

Результаты тестирования

www.laduga.com

Глава 1. Заданные параметры теста

Название тестируемого компонента

VariableRateLimiter

Модуль тестируемого компонента

Signals

Дата тестирования

Thu Mar 12 18:46:33 2026

Результат

OK

Глава 2. Схема тестируемого объекта

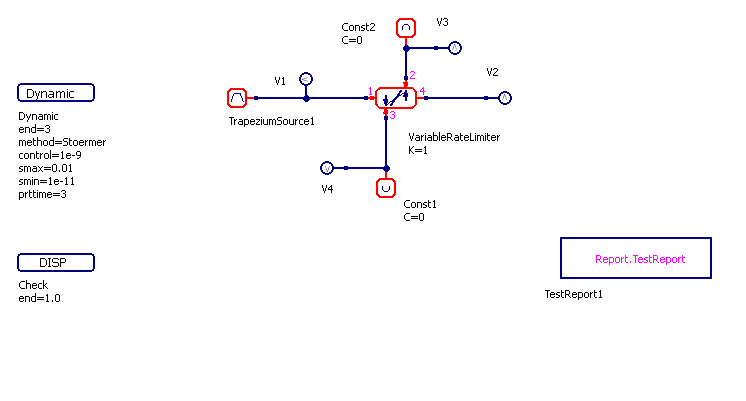

Схема тестирования: Модель ограничения скорости сигнала (VariableRateLimiter)

Изменение формы сигнала при параметризации элемента преобразования.

Исодный сигнал проходит через преобразователь сигнала, датчик V1 считывает

исходный сигнал, V2 - сигнал на выходе,

V3 и V4 - уровни сигналов ограничения.

Сигналы, ограничивающие изменение исходного сигнала Const1 и Const2.

Исходные данные (баз):

Коэфф. усиления сигнала K=1

Сигналы ограничения

1. Значение константы С=0

2. Значение константы С=0

Амплитуда А=1

Время интеграции end=3

Результат: При уровнях 1го и 2го сигналов ограничения С=0, преобразованный сигнал = 0

Исходный сигнал - трапецеидальный.

Рисунок 1 - Схема теста

Глава 3. Графики результатов теста

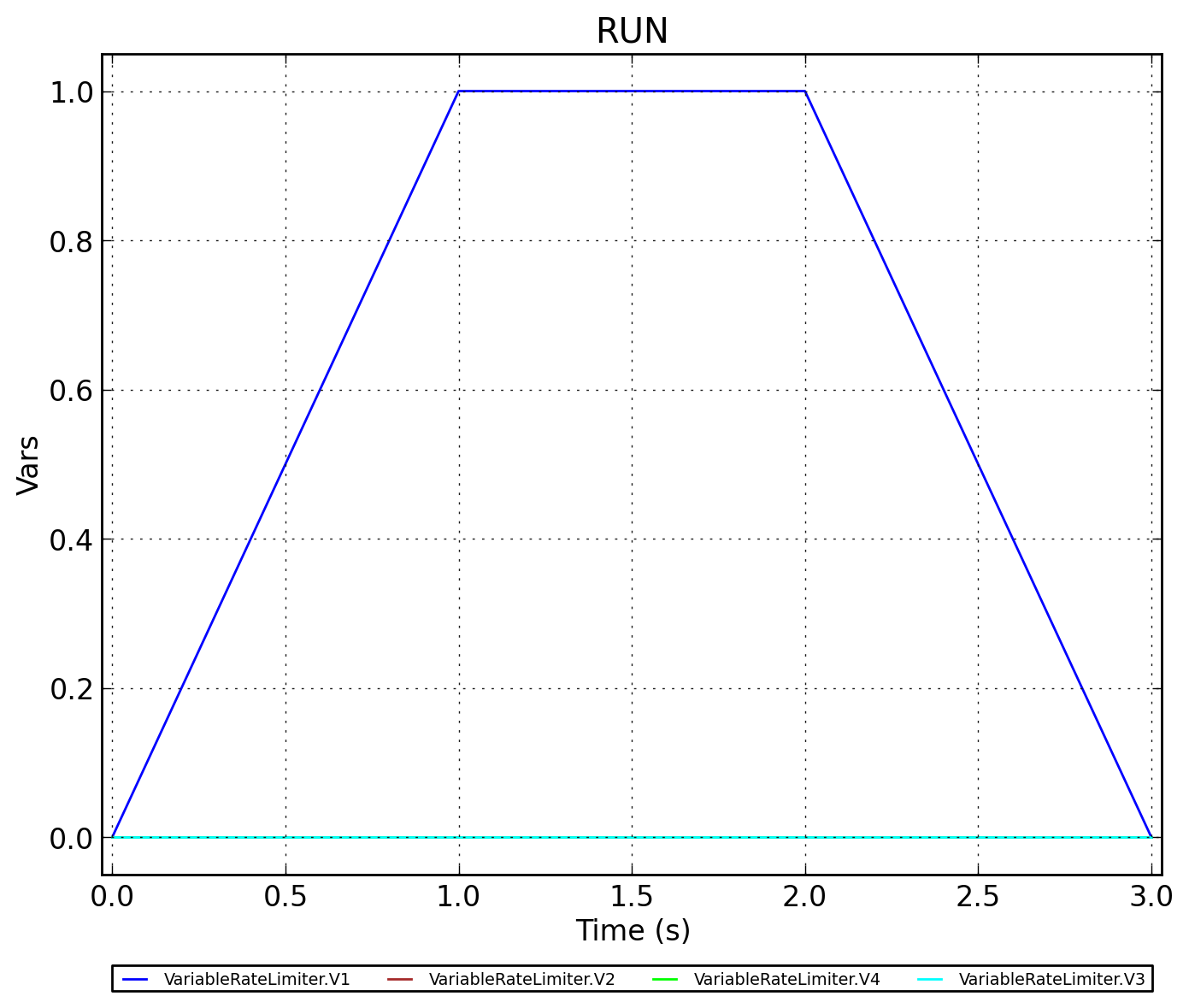

Рисунок 2 - VariableRateLimiter.RUN

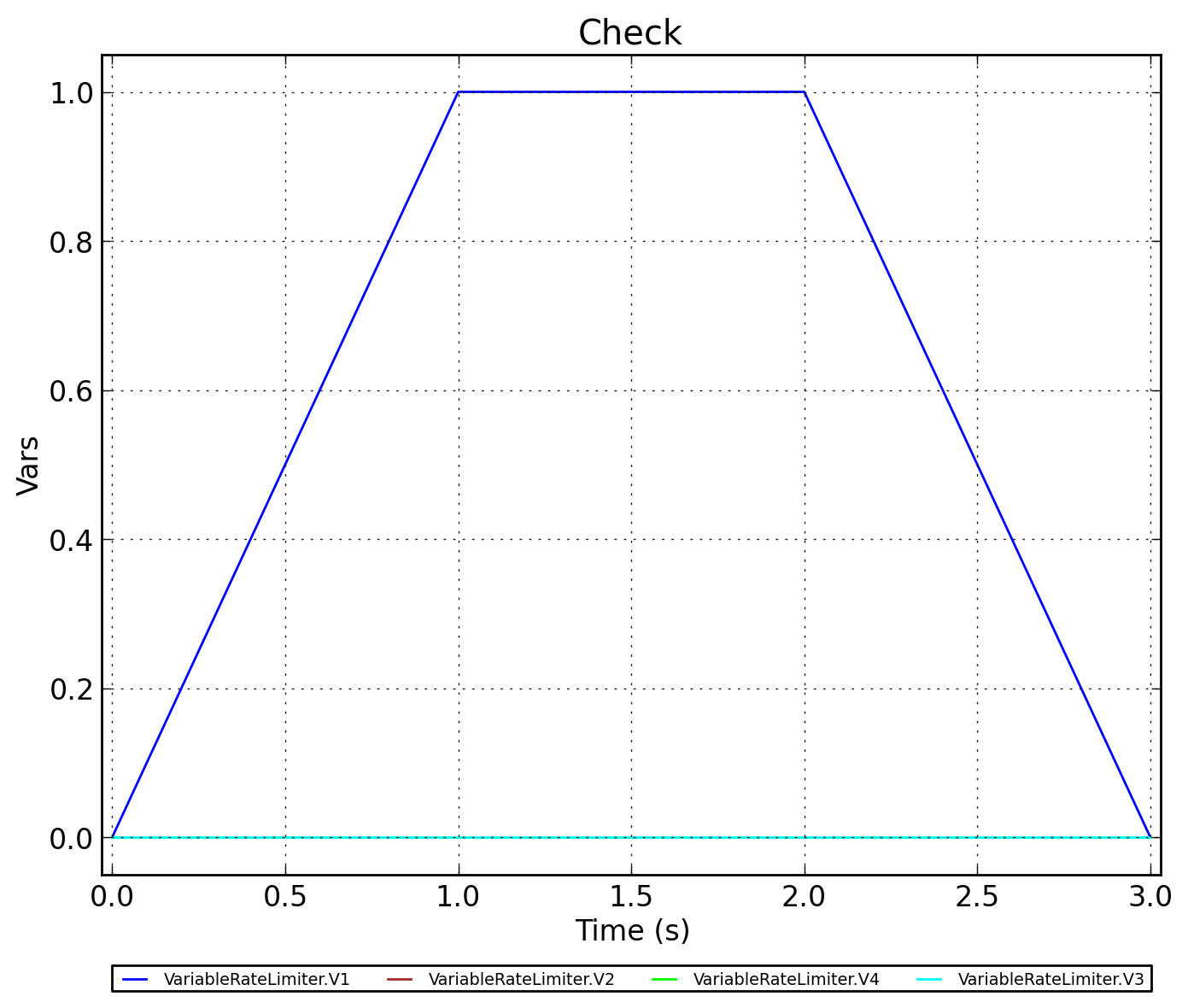

Рисунок 3 - VariableRateLimiter.Check